Description

In this course, you will :

- How do people manage to create such complex chips? The answer is that a series of computer-aided design (CAD) tools takes an abstract description of the chip and refines it step by step to a final design.

- focuses on the major design tools used in the development of an Application Specific Integrated Circuit (ASIC) or System on Chip (SoC).

- Concentrate on the key logical and geometric representations that allow you to map from logic to layout, and more specifically, to place, route, and evaluate the timing of large logic networks.

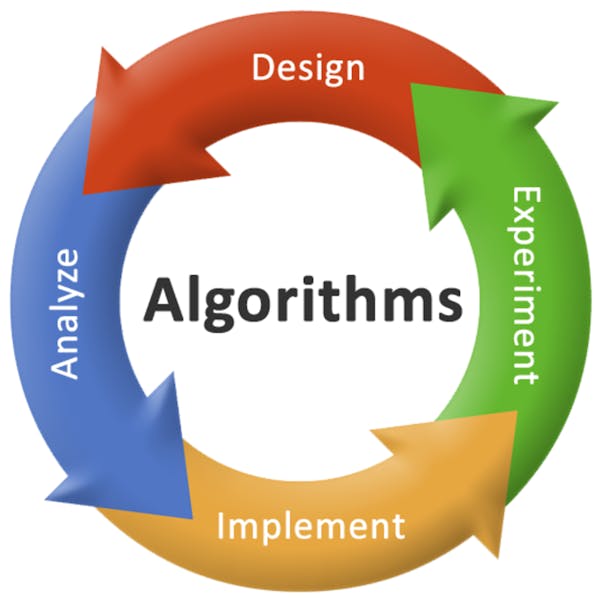

- understand how the tools themselves work, down to their basic algorithms and data structures

- Technology mapping, timing analysis, and ASIC placement and routing will be among the topics covered.

Syllabus :

1. ASIC Placement

- Wirelength Estimation

- Simple Iterative Improvement Placement

- Iterative Improvement with Hill Climbing

- Simulated Annealing Placement

- Analytical Placement: Quadratic Wirelength Model

- Quadratic Placement

- Recursive Partitioning

- Recursive Partitioning Example

2. Technology Mapping

- Technology Mapping as Tree Covering

- Technology Mapping—Tree-ifying the Netlist

- Recursive Matching

- Minimum Cost Covering

- Detailed Covering Example

3. ASIC Routing

- Maze Routing: 2-Point Nets in 1 Layer

- Maze Routing: Multi-Point Nets

- Layer Routing

- Maze Routing: Non-Uniform Grid Costs

- Implementation Mechanics: How Expansion Works

- Data Structures & Constraints

- Depth First Search

- From Detailed Routing to Global Routing

4. Timing Analysis

- Logic-Level Timing: Basic Assumptions & Models

- STA Delay Graph, ATs, RATs, and Slacks

- A Detailed Example and the Role of Slack

- Computing ATs, RATs, Slacks, and Worst Paths

- Electrical Models of Wire Delay

- The Elmore Delay Model

- Elmore Delay Examples